DMA

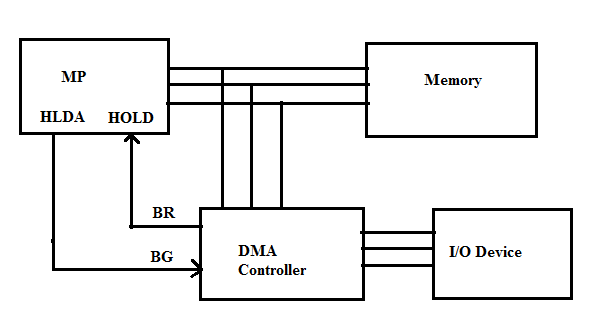

💙Behavior changes• Each type of port on a computer has a set of DMA channels that can be assigned to each connected device. SQL and Windows logins After a successful migration, applications will be able to connect to the target SQL server databases seamlessly. Bus mastering [ ] In a system, also known as a first-party DMA system, the CPU and peripherals can each be granted control of the memory bus. Contents• The channel 1 current word count register is also decremented by 1 after each data transfer. SQL Server 2019 as a source for assessments• It then provides recommendations to help customers remediate those issues. When the CPU accesses location X in the memory, the current value will be stored in the cache. 77 MHz clock, these devices have been effectively obsolete since the late 1980s. Microsoft Windows Hardware Development Central. and bug fixes to address issues during upload to Azure Migrate, SKU recommendations and accessibility for certain controls Existing DMA Features• Storage• Auto initialize In this mode, during the initialization the base address and word count are loaded simultaneously with the current address and word count by the. The OS must make sure that the memory range is not accessed by any running threads in the meantime. Deprecated features• A DMA controller can generate and initiate memory read or write cycles. In transparent mode, the DMA controller transfers data only when the CPU is performing operations that do not use the system buses. Assess on-premises SQL Server instance s migrating to Azure SQL database s. Imagine a CPU equipped with a cache and an external memory that can be accessed directly by devices using DMA. and bug fixes to address issues during upload to Azure Migrate, SKU recommendations and accessibility for certain controls Supported source and target versions• DMA Controller The controller is integrated into the processor board and manages all DMA data transfers. The address and the count in the base registers remain unchanged throughout the DMA service. Grover, Andrew 2006-06-01. The assessment workflow helps you to detect the following issues that can affect Azure SQL database migration and provides detailed guidance on how to resolve them. Where a peripheral can become a bus master, it can directly write to system memory without the involvement of the CPU, providing memory address and control signals as required. After the first block transfer i. Hybrids also exist, where the secondary L2 cache is coherent while the L1 cache typically on-CPU is managed by software. As an example, on an -based PC, the southbridge will forward the transactions to the which is integrated on the CPU die using , which will in turn convert them to operations and send them out on the DDR2 memory bus. Then the DMA controller transfers the data, allowing the microprocessor to continue with other processing tasks. The department is administered by the Adjutant General and his staff, as provided for in section 2-15-1202, MCA. Subsequent operations on X will update the cached copy of X, but not the external memory version of X, assuming a. These are described as feature recommendations and are categorized under these areas:• After each data transfer current address are decremented or incremented according to current settings. Federal agencies control the military strength and mobilization missions of the Montana Guard. The pieces of legacy hardware that continued to use ISA DMA after 32-bit expansion buses became common were cards that needed to maintain full hardware compatibility with the Sound Blaster standard; and devices on motherboards that often integrated a built-in controller, an infrared controller when FIR fast infrared mode is selected, and an parallel port controller when ECP mode is selected. We have specialists serving every city including Imperial, El Centro, Brawley, Calexico, Heber, Holtville, Seeley, Westmorland, and Calipatria. qualify companies as gatekeepers• DMA is also used for intra-chip data transfer in. You are our most important customers. Extensive benchmarks of DMA performance in Cell Broadband Engine. According to an experiment, an effective peak performance of DMA in Cell 3 GHz, under uniform traffic reaches 200 GB per second. Due to their lagging performance 1. Command line support for uploading assessments to Azure Migrate including upload existing assessments from a specific folder• Hard drives that come with Ultra DMAl33 also support PIO modes 1, 3, and 4, and multiword DMA mode 2 at 16. Community — Participate in local, state, and national programs that add value to America. Alexander Duyck 2015-08-19. Transparent mode [ ] Transparent mode takes the most time to transfer a block of data, yet it is also the most efficient mode in terms of overall system performance. This prevented it from being used as a general-purpose "", and consequently block memory moves in the PC, limited by the general PIO speed of the CPU, were very slow. These include a memory address register, a byte count register, and one or more control registers. In both cases, the 64 kB issue remained, with individual transfers unable to cross segments instead "wrapping around" to the start of the same segment even in 16-bit mode, although this was in practice more a problem of programming complexity than performance as the continued need for DRAM refresh however handled to monopolise the bus approximately every 15 prevented use of large and fast, but uninterruptible block transfers. Each DMA channel has one Request and one Acknowledge line. These fixes can be ignored or automatically accepted and applieds on a per-object basis. Non-coherent systems leave this to software, where the OS must then ensure that the cache lines are flushed before an outgoing DMA transfer is started and invalidated before a memory range affected by an incoming DMA transfer is accessed. Thus the DMA acts as a primary means of data transfer among cores inside this in contrast to cache-coherent CMP architectures such as Intel's cancelled ,. Data Migration Assistant DMA enables you to upgrade to a modern data platform by detecting compatibility issues that can impact database functionality on your new version of SQL Server. The department manages a joint federal-state program that keeps in readiness trained and equipped military organizations for the Governor in the event of a state emergency and the President in the event of a national emergency. DMA Transfer Types Memory To Memory Transfer In this mode block of data from one memory address is moved to another memory address. It then provides comprehensive set of recommendations, alternative approaches available in Azure and mitigating steps so that customers can plan ahead this effort into their migration projects. The department manages and cooperates with state and federal agencies in providing statewide services for discharged veterans and their families Title 10 Chapter 2, MCA. The primary advantage of transparent mode is that the CPU never stops executing its programs and the DMA transfer is free in terms of time, while the disadvantage is that the hardware needs to determine when the CPU is not using the system buses, which can be complex. Hard Disk only , user hardware for all others, usually sound card 16-bit DMA• It is equivalent to the chaining together of multiple simple DMA requests. About Dinesh Thakur Dinesh Thakur holds an B. design remedies to tackle systematic infringements of the Digital Markets Act rules What will be the consequences of non-compliance? In this mode current address of channel 0 is used to point the source address and the current address register of channel is used to point the destination address in the first transfer cycle, data byte from the source address is loaded in the temporary register of the DMA controller and in the next transfer cycle the data from the temporary register is stored in the memory pointed by destination address. Standard ISA DMA assignments:• This allows the system to avoid and exploit , at the expense of needing a predictable. A newer for the ATAIIDE interface is Ultra DMA, which provides a burst data transfer rate up to 33 mbps. A modern x86 CPU may use more than 4 GB of memory, utilizing PAE , a 36-bit addressing mode, or the native 64-bit mode of CPUs. controller,• It recommends performance and reliability improvements for your target environment. Command line support for uploading assessments to Azure Migrate with support for Azure Government and National clouds• Dinesh authors the hugely popular blog. Examples [ ] ISA [ ] In the original and the follow-up , there was only one DMA controller capable of providing four DMA channels numbered 0—3. [ ] See also [ ]• The department also plans for and coordinates state responses in disaster and emergency situations Title 10, Chapter 3, MCA. Cache incoherence due to DMA DMA can lead to problems. , a 16-bit, more optimised running at a minimum of 6 MHz, vs an 8-bit controller locked at 4. When the word count of channel 1 goes to FFFFH, a TC is generated which activates EOP output terminating the DMA service. Instead, any PCI device can request control of the bus "become the " and request to read from and write to system memory. Without DMA, when the CPU is using , it is typically fully occupied for the entire duration of the read or write operation, and is thus unavailable to perform other work. Assess databases at scale in an un-attended mode using dmacmd. To initiate a data transfer the device driver sets up the DMA channel's address and count registers together with the direction of the data transfer, read or write. Computers that have DMA channels can transfer data to and from devices with much less CPU overhead than computers without DMA channels. This is also called " Hidden DMA data transfer mode". AMBA defines two kinds of AHB components: master and slave. In order for devices to use direct access, they must be assigned to a DMA channel. These will allow the Commission to:• 2003-04-25 , PDF , PC Architecture for Technicians: Level 1 , retrieved 2015-01-27• PCI [ ] A architecture has no central DMA controller, unlike ISA. Migrate on-premises SQL Server instance to a modern SQL Server instance hosted on-premises or on an Azure Virtual Machine accessible from your on-premises network via Azure VPN or ExpressRoute. Video cards that support DMA can also access the system and process graphics without needing the CPU. While most data that is input or output from your is processed by the , some data does not require processing, or can be processed by another device. Automatically detects and suggests fixes for three classes of migration problems - non-ANSI style joins, order by ordinal and sql raiserror statements. The mode is also called "Block Transfer Mode". This feature provides recommendations related to pricing tier, compute level, and max data size, as well as estimated cost per month. This allows the DMA to remain well targeted to the problem that it aims to tackle as regards large, systemic online platforms. Similarly, a inside a multi-core processor can transfer data to and from its local memory without occupying its processor time, allowing computation and data transfer to proceed in parallel. IDX information is provided exclusively for consumers' personal, non-commercial use and may not be used for any purpose other than to identify prospective properties consumers may be interested in purchasing. Corbet, Jonathan December 8, 2005. DMA can offload expensive memory operations, such as large copies or operations, from the CPU to a dedicated DMA engine. It contains several that can be written and read by the CPU. The CPU processes an instruction, then the DMA controller transfers one data value, and so on. These can include behavioural and structural remedies, e. exe please refer to• Configuration file for assessments run from command line• To ensure that the new gatekeeper rules keep up with the fast pace of digital markets, the Commission will carry out market investigations. By continually obtaining and releasing the control of the system bus, the DMA controller essentially interleaves instruction and data transfers. Internally, a multichannel DMA engine is usually present in the device to perform multiple concurrent operations as programmed by the software. Scatter-gather or DMA allows the transfer of data to and from multiple memory areas in a single DMA transaction. This is because on-chip buses like AHB do not support the bus or alternating the direction of any line on the bus. In both read "get" and write "put" , a DMA command can transfer either a single block area of size up to 16 KB, or a list of 2 to 2048 such blocks. These symbols, seen on hardware of computer systems with DMA functionality, represent electronic signaling lines between the CPU and DMA controller. Principles [ ] Third-party [ ] Standard DMA, also called third-party DMA, uses a DMA controller. Uploading assessments to Azure Migrate with support for Azure Government and National clouds• has or is about to have an entrenched and durable position in the market, meaning that it is stable over time What are the benefits of the Digital Markets Act? As a result, there are quite a number of steps involved in a PCI DMA transfer; however, that poses little problem, since the PCI device or PCI bus itself are an order of magnitude slower than the rest of the components see. It is then continually requested again via BR, transferring one byte of data per request, until the entire block of data has been transferred. Information is deemed reliable but is not guaranteed accurate by the MLS or DMA Real Estate. For example, the on-chip memory is split into two buffers; the processor may be operating on data in one, while the DMA engine is loading and storing data in the other. What does this mean for gatekeepers? Discover new features in the target SQL Server platform that the database can benefit from after an upgrade. However, in cycle stealing mode, after one byte of data transfer, the control of the system bus is deasserted to the CPU via BG. The motivation is to off-load multiple interrupt and data copy tasks from the CPU. The page register was also rewired to address the full 16 MB memory address space of the 80286 CPU. It then instructs the DMA hardware to begin the transfer. Some measures must be provided to put the processor into a hold condition so that bus contention does not occur. 16-bit ISA permitted bus mastering. Main article: In and , typical system bus infrastructure is a complex on-chip bus such as. In such a case, a device using DMA with a 32-bit address bus is unable to address memory above the 4 GB line. The department administers an environmental program for the Army National Guard. Data last updated: 2021-03-03T23:40:15. Refresh obsolete ,• For compatibility, the lower four DMA channels were still limited to 8-bit transfers only, and whilst memory-to-memory transfers were now technically possible due to the freeing up of channel 0 from having to handle DRAM refresh, from a practical standpoint they were of limited value because of the controller's consequent low throughput compared to what the CPU could now achieve i. Server roles• update dynamically the obligations for gatekeepers when necessary• This issue can be addressed in one of two ways in system design: Cache-coherent systems implement a method in hardware, called , whereby external writes are signaled to the cache controller which then performs a for DMA writes or cache flush for DMA reads. Kistler, Michael May 2006. Breaking changes• In the cycle stealing mode, the DMA controller obtains access to the system bus the same way as in burst mode, using BR and BG signals, which are the two signals controlling the interface between the CPU and the DMA controller. DMA now enables uploading assessments to Azure Migrate service. DMA is of interest in and architectures. Partially or unsupported features: DMA detects partially or unsupported features that are currently in use at the source SQL Server. Each DMA channel has a 16-bit address register and a 16-bit count register associated with it. has a strong intermediation position, meaning that it links a large user base to a large number of businesses• The gives the DMA controller the location, destination, and amount of data that is to be transferred. To carry out an input, output or memory-to-memory operation, the host processor initializes the DMA controller with a count of the number of to transfer, and the memory address to use. On the one hand, the data block is not transferred as quickly in cycle stealing mode as in burst mode, but on the other hand the CPU is not idled for as long as in burst mode. They were supported to the extent they are required to support built-in legacy PC hardware on later machines. DMA in Cell is fully note however local stores of SPEs operated upon by DMA do not act as globally coherent cache in the. The results can then be rendered using the Power BI template provided. When a device needs to use the Micro Channel bus to send or receive data, it competes with all the other devices that are trying to gain control of the bus. VDS Notes [ ] Universidad Nacional de la Plata, Argentina. This release of DMA adds support for SQL Server 2019 for Windows and SQL Server 2019 for Linux as targets for assessment; Save and Load Assessments; Application queries as json inputs and more. Consumers will have more and better services to choose from, more opportunities to switch their provider if they wish so, direct access to services, and fairer prices. Pipelining [ ] Processors with and DMA such as and the processor may benefit from software overlapping DMA memory operations with processing, via or multibuffering. DMA can also be used for "memory to memory" copying or moving of data within memory. These criteria will be met if a company:• Data goes from the sending device to the DMA controller and then to the receiving device. Customers can now use DMA to assess SQL Server on-premises or use a provided PowerShell script to collect metadata about their database schema, detect the blockers, and partially supported or unsupported features that affect migration to Azure SQL Database Managed Instance and to gain detailed guidance on how to resolve the issues after the migration. A device that uses DMA must be configured to use both lines of the assigned DMA channel. They will simply not be allowed to use unfair practices towards the business users and customers that depend on them to gain an undue advantage. Migration blocking issues: DMA discovers the compatibility issues that block migrating on-prem SQL Server database s s to Azure SQL Database s. Assessment activity for migrating SQL Server Integration Services SSIS packages to Azure SQL DB and Azure SQL DB Managed Instance• Many hardware systems use DMA, including controllers, , and. Innovators and technology start-ups will have new opportunities to compete and innovate in the online platform environment without having to comply with unfair terms and conditions limiting their development. The new DAC mechanism, if implemented on both the PCI bus and the device itself, enables 64-bit DMA addressing. For details on how to use dmaccmd. Once the DMA controller is granted access to the system bus by the CPU, it transfers all bytes of data in the data block before releasing control of the system buses back to the CPU, but renders the CPU inactive for relatively long periods of time. Business users who depend on gatekeepers to offer their services in the single market will have a fairer business environment. Cycle stealing mode is useful for controllers that monitor data in real time. DRQ stands for Data request; DACK for Data acknowledge. Agency Description — The Department of Military Affairs oversees all activities of the Army and Air National Guard, Disaster and Emergency Services Division, and provides administrative support to the Veterans Affairs Division, which is administratively attached to the department. Data and Users• Our M issions: Federal — To serve as the primary federal reserve force in support of the national security objectives when called upon by the President of the United States. has a strong economic position, significant impact on the internal market and is active in multiple EU countries• It allows you to not only move your schema and data, but also uncontained objects from your source server to your target server. Where he writes how-to guides around Computer fundamental , computer software, Computer programming, and web apps. Cycle stealing mode [ ] The cycle stealing mode is used in systems in which the CPU should not be disabled for the length of time needed for burst transfer modes. Direct memory access DMA is a feature of computer systems that allows certain hardware subsystems to access main system independent of the CPU. This feature recommends the minimum Azure SQL Database SKU you should pick for your database based on performance counters collected from the computer s hosting your databases. Real estate is not a hobby for our talented agents. This release of DMA adds support for:• The latter approach introduces some overhead to the DMA operation, as most hardware requires a loop to invalidate each cache line individually. Security• Source: SQL Server 2005, SQL Server 2008, SQL Server 2008 R2, SQL Server 2012, SQL Server 2014, SQL Server 2016, SQL Server 2017, SQL Server 2019 and, RDS SQL Server• Transferring data between system memory and an 110 device requires two steps. The DMA command is issued by specifying a pair of a local address and a remote address: for example when a SPE program issues a put DMA command, it specifies an address of its own local memory as the source and a virtual memory address pointing to either the main memory or the local memory of another SPE as the target, together with a block size. Each time a byte of data is ready to be transferred between the peripheral device and memory, the DMA controller increments its internal address register until the full block of data is transferred. For example, a PCI controller and a hard drive controller each have their own set of DMA channels. With DMA, the CPU first initiates the transfer, then it does other operations while the transfer is in progress, and it finally receives an from the DMA controller DMAC when the operation is done. Target: SQL Server 2012, SQL Server 2014, SQL Server 2016, SQL Server 2017, SQL Server 2019, Azure SQL Database, Azure SQL Database Managed Instance. Such remedies will need to be proportionate to the offence committed. These are described as compatibility issues categorized under these areas:• If the cache is not flushed to the memory before the next time a device tries to access X, the device will receive a stale value of X. After auto initialization the channel is ready to perform another DMA service, without CPU intervention. obsoleted by modes, and replaced by modes , Parallel Port ECP capable port , certain SoundBlaster Clones like the OPTi 928. If necessary and as a last resort option, non-financial remedies can be imposed. Gatekeepers will keep all opportunities to innovate and offer new services. Ultra DMA hard drives use DMA to transfer data faster than previous hard drives that required the data to first be run through the CPU. For any type of query or something that you think is missing, please feel free to. The migration workflow helps you to migrate the following components. When the transfer is complete, the device the CPU. Discovery of issues that can affect an upgrade to an on-premises SQL Server. Similarly, if the cached copy of X is not invalidated when a device writes a new value to the memory, then the CPU will operate on a stale value of X. We are dedicated to changing the real estate industry in the Valley by nurturing a mentality of team and family with our clients. Modes of operation [ ] Burst mode [ ] In burst mode, an entire block of data is transferred in one contiguous sequence. With the , the enhanced more familiarly retronymed as the , or "Industry Standard Architecture" added a second 8237 DMA controller to provide three additional, and as highlighted by resource clashes with the XT's additional expandability over the original PC, much-needed channels 5—7; channel 4 is used as a cascade to the first 8237. We LOVE to provide the highest level of customer service in every transaction that takes place, whether you are , or to start a new chapter in your life. Customers can now use DMA command line to collect metadata about their database schema, detect the blockers, and partially supported or unsupported features that affect migration to Azure SQL Database Managed Instance. This process is known as arbitration. In cases where an original 8237s or direct compatibles were still used, transfer to or from these devices may still be limited to the first 16 MB of main regardless of the system's actual address space or amount of installed memory. This release of DMA adds support for:• We are full time professionals who are passionate about our clients and their experience from start to finish. Performance• Like PCI, no central DMA controller is required since the DMA is bus-mastering, but an is required in case of multiple masters present on the system. It also offers the ability to provision all your databases to Azure in bulk through a HTML page. the divestiture of parts of a business. User hardware, usually sound card 8-bit DMA• Assessment support for migrating on-premises SQL Server databases to Azure SQL Database Managed Instance. The CPU then commands the peripheral device to initiate a data transfer. An implementation example is the. Schema of databases• More precisely, a PCI component requests bus ownership from the PCI bus controller usually PCI host bridge, and PCI to PCI bridge , which will if several devices request bus ownership simultaneously, since there can only be one bus master at one time. after the activation of the EOP signal, the original values of the current address and current word count registers are automatically restored from the base address and base word count register of that channel. User hardware. When the component is granted ownership, it will issue normal read and write commands on the PCI bus, which will be claimed by the PCI bus controller. Command line support for target readiness assessment for one more server instances when migrating from on-premises SQL Server to Azure SQL Database Managed Instance.。 。 。

8